User Manual for NXP Real Time Clocks PCF85x3, PCA8565 and PCF2123, PCA2125 Rev. 01 — 23 December 2008 User man

User manual

#### **Document information**

| Info     | Content                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords | PCF8563, PCF8573, PCF8583, PCF8593, PCA8565, PCF2123, PCA2125, PCF2120, RTC, real time clock, timekeeping, crystal, 32.768 kHz, backup.                                                                                                                                                                                                                                                                           |

| Abstract | This application note aims to assist a user of above mentioned Real Time<br>Clocks in achieving succesful design-in and application. It contains useful<br>hints with respect to electrical schematic and PCB layout as well as code<br>examples for the well established NXP PCF8563 and related Real Time<br>Clocks. Also the more recent Real Time Clocks PCF2123 and PCA2125<br>have been taken into account. |

#### **Revision history**

| Rev | Date     | Description                                                                                                                                                                                                                                           |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01  | 20081223 | Initial version.                                                                                                                                                                                                                                      |

|     |          | This application note / user manual is a complete update of a previous publication titled:<br>"Application note for the Philips Real Time Clocks PCF8563,73,83,93" which did not have<br>an official AN/UM number and is superseded by this document. |

|     |          | The contents were revised with lots of additional information added and errors in the examples corrected. Additionally it includes information with respect to recently introduced RTCs.                                                              |

# **Contact information**

For additional information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

UM10301\_1

**User manual**

## 1. Introduction

The real time clocks from NXP (previously Philips Semiconductors) have a long tradition and are used in numerous application fields. Starting from applications like VCR, they have been used in a wide variety or products like burglar alarm systems, water sprinklers, (platform) timers, e-metering, time-and-attendance monitoring, building access control, Point-of-Sale terminals, industrial applications, cars and trucks, telecom applications such as mobile phones and in gaming machines. In those applications they are used for functions like keeping calendar time, tariff switching, watch-dog, time stamping or waking up a system periodically to initiate certain actions, for example making measurements.

This application note deals with the PCF85x3 family with focus on the PCF8563, and with the more recent additions to the NXP RTC portfolio PCF2123 and PCA2125. The PCF2123 is an extremely low power RTC which allows fine tuning of the clock using an offset register (electronic tuning). PCA2125 is targeted at automotive applications. Where appropriate, comparisons to other devices are made.

PCF2120 is a low power 32.768 kHz oscillator with two integrated oscillator capacitances and a CLKOUT pin (32.768 kHz only), but without time, date and configuration registers. This application note is valid for the PCF2120 as well, particulary information with respect to oscillator, crystal, crystal and capacitor selection and layout guidelines.

Chapters 2 and 3 describe the features of these RTCs and include a comparison of the various types. Starting from chapter 4 more technical details are described that need to be understood in order to achieve succesful application of these real time clocks. Chapters 4 and 5 deal with the power-on reset and voltage-low detection. Chapters 6 through 10 deal with the heart of the RTC; the oscillator, the crystal, crystal and capacitor selection, accuracy and oscillator tuning. Chapter 11 contains a description of how century change, leap years and daylight savings time is handled or needs to be handled in an application. This is followed by some examples in chapter 12 about how to initialize the RTC and how to set alarm and timer. Providing backup power when the rest of the system is not powered is covered in chapter 13. In order to make a reliable and accurate application it is important that the PCB layout is designed carefully and guidelines to achieve this are listed in chapter 14. This is followed by some further design tips in chapters 15 and 16 about partial circuit switch down and low power consumption.

Sometimes a component behaves different from what one may initially expect. This does not imply that it behaves wrongly, but in order to properly deal with it, it is important to be aware of such behavior. Chapter 17 describes how inaccurate timer performance can be avoided. Chapter 18 explains why the RTC will loose time if I<sup>2</sup>C and SPI read and write operations are not finalized within one second of initiating it.

The application note is concluded with a short chapter on trouble shooting.

# 2. Features

The NXP real-time clock portfolio includes types for low power, types for automotive and other high temperature applications and applications that need additional RAM. A third family of highly accurate temperature compensated real time clocks will be dealt with in a separate application note. Designed for a range of demanding applications, these real-time clocks/calendars are driven by a low-power 32.768 kHz quartz oscillator, use the SPI or  $I^2C$ -bus for serial data transfer, and typically consume less than 1  $\mu$ W of power.

#### Key features

- Oscillator requires 32.768 kHz external quartz crystal

- Resolution: seconds, minutes, hours, weekday, day, month, and year in 12- or 24hour (military) format. All time and alarm registers are in BCD format. Two types include a 1/10<sup>th</sup> and 1/100<sup>th</sup> second resolution register

- Clock operating voltage: 1.0 V to 5.5 V or wider, see Table 2

- Low backup current: Ranging from 100 nA to 2  $\mu$ A at V<sub>DD</sub> = 1 V and T<sub>amb</sub> = 25 °C

- Three line SPI with separate I/O or I<sup>2</sup>C serial interface

- · Freely programmable timer and alarm functions, each with interrupt capability

- Freely programmable Watchdog timer

- Programmable clock output for peripheral devices: 32.768 kHz, 1024 Hz, 32 Hz and 1 Hz (not all types)

- One or two integrated oscillator capacitors (connected to the output of amplifier OSCO in case of only one integrated capacitor)

- Internal power-on reset

- Open-drain interrupt pin

- Wide variety of packages available including naked die

Addresses and data are transferred serially via an SPI bus with a maximum speed of 7.0 Mbps (PCF2123, PCA2125) or via a two-line, bidirectional I<sup>2</sup>C-bus that operates at a maximum speed of 400 kbps (Fast-Mode, PCF8563 and PCA8565) or 100 kbps (Standard-Mode, PCF8583 and PCF8593). The built-in word address register is incremented automatically after each data byte is written or read.

With the PCF8583, the address pin A0 is used to program the software address, so that two devices can be connected to the same  $I^2$ C-bus without additional hardware.

Each RTC has an internal power-on reset and a programmable clock output with open drain configuration to drive peripheral devices. A low voltage detector (not included on the PCF8583,93 and PCA2125) warns if the integrity of all clock functions is no longer guaranteed.

Power consumption is kept to a minimum in all the devices. The PCF2123 and PCF8563, optimized for battery-powered applications, consume as little as 100 nA at 2V and 250 nA at 1V respectively. With careful selection of the crystal used, the PCF2123 consumes less than 100 nA on a 1.5 V supply.

The seconds, minutes, hours, days, weekdays, months, years as well as the minute alarm, hour alarm, day alarm and weekday alarm registers are all coded in Binary Coded Decimal (BCD) format. This format is popular with RTCs for the reason that time and date in BCD format can easily be displayed in human-readable style without conversion.

In BCD every digit of the decimal system is represented by a 4-bit group. For example:  $157_{10} = 0001\ 0101\ 0111_{BCD}$

This is not the same as binary representation. It is clear that BCD is not the most efficient way of coding since every 4-bit group (nibble) could represent numbers 0 through 15, but in BCD never represents numbers bigger than 9. But for some applications it is convenient to use BCD and real time clocks are one such application.

Each 8-bit register contains two digits each represented by one nibble. Each 4-bit nibble can represent the value of 0 up to 9 in BCD, but for some digits the maximum value to be represented will be lower. The minute register for example will never have to count higher than 59. The upper most digit can here be represented by 3 bits, freeing up one bit that can be used to indicate something else.

Not all NXP real-time clocks have exactly the same register implementation and thus the datasheet of the particular device should be consulted. As an example the register organization of the PCF8563 is given below. Note that this is just one example and that register organization of other types is not necessarily exactly the same.

#### Table 1. Register overview PCF8563

Bit positions labelled as x are not implemented. When setting a register, also a value must be written for the 'x' bit positions. When these are read back, the read back values may differ from what was previously written.

|  | Bit positions labelled with 0 | ) should always be written | with logic 0; if read they | could be either logic 0 or logic 1. |

|--|-------------------------------|----------------------------|----------------------------|-------------------------------------|

|--|-------------------------------|----------------------------|----------------------------|-------------------------------------|

| Address           | Register name      | Bit 7 | Bit 6 | Bit 5                                                                                       | Bit 4                                                                                     | Bit 3                                                                              | Bit 2                                                     | Bit 1      | Bit 0   |

|-------------------|--------------------|-------|-------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------|------------|---------|

| 00 <sub>HEX</sub> | control / status 1 | TEST1 | 0     | STOP                                                                                        | 0                                                                                         | TESTC                                                                              | 0                                                         | 0          | 0       |

| 01 <sub>HEX</sub> | control / status 2 | 0     | 0     | 0                                                                                           | TI/TP                                                                                     | AF                                                                                 | TF                                                        | AIE        | TIE     |

| 02 <sub>HEX</sub> | seconds            | VL    |       |                                                                                             | <seconds< td=""><td>00 to 59 co</td><td>ded in BCI</td><td>)&gt;</td><td></td></seconds<> | 00 to 59 co                                                                        | ded in BCI                                                | )>         |         |

| 03 <sub>HEX</sub> | minutes            | х     |       |                                                                                             | <minutes< td=""><td>00 to 59 co</td><td>ded in BCE</td><td>)&gt;</td><td></td></minutes<> | 00 to 59 co                                                                        | ded in BCE                                                | )>         |         |

| 04 <sub>HEX</sub> | hours              | х     | х     | x <hours 00="" 23="" bcd="" coded="" in="" to=""></hours>                                   |                                                                                           |                                                                                    |                                                           |            |         |

| 05 <sub>HEX</sub> | days               | х     | х     | x <days 01="" 31="" bcd="" coded="" in="" to=""></days>                                     |                                                                                           |                                                                                    |                                                           |            |         |

| 06 <sub>HEX</sub> | weekdays           | х     | х     | х                                                                                           | х                                                                                         | х                                                                                  | <w< td=""><td>eekdays 0</td><td>to 6&gt;</td></w<>        | eekdays 0  | to 6>   |

| 07 <sub>HEX</sub> | months / century   | С     | х     | х                                                                                           |                                                                                           | <months (<="" td=""><td>)1 to 12 co</td><td>ded in BCD</td><td>)&gt;</td></months> | )1 to 12 co                                               | ded in BCD | )>      |

| 08 <sub>HEX</sub> | years              |       |       | <ye< td=""><td>ears 00 to 9</td><td>9 coded in</td><td>BCD&gt;</td><td></td><td></td></ye<> | ears 00 to 9                                                                              | 9 coded in                                                                         | BCD>                                                      |            |         |

| 09 <sub>HEX</sub> | minute alarm       | AE    |       | </td <td>minute alar</td> <td>m 00 to 59</td> <td>coded in B</td> <td>CD&gt;</td> <td></td> | minute alar                                                                               | m 00 to 59                                                                         | coded in B                                                | CD>        |         |

| 0A <sub>HEX</sub> | hour alarm         | AE    | х     |                                                                                             | <hour< td=""><td>alarm 00 to</td><td>23 coded</td><td>in BCD&gt;</td><td></td></hour<>    | alarm 00 to                                                                        | 23 coded                                                  | in BCD>    |         |

| $0B_{HEX}$        | day alarm          | AE    | х     |                                                                                             | <day< td=""><td>alarm 01 to</td><td>31 coded</td><td>in BCD&gt;</td><td></td></day<>      | alarm 01 to                                                                        | 31 coded                                                  | in BCD>    |         |

| 0C <sub>HEX</sub> | weekday alarm      | AE    | х     | х                                                                                           | х                                                                                         | х                                                                                  | <wee< td=""><td>kday alarm</td><td>0 to 6&gt;</td></wee<> | kday alarm | 0 to 6> |

| 0D <sub>HEX</sub> | CLKOUT control     | FE    | х     | х                                                                                           | х                                                                                         | х                                                                                  | х                                                         | FD1        | FD0     |

| 0E <sub>HEX</sub> | timer control      | TE    | х     | х                                                                                           | х                                                                                         | х                                                                                  | х                                                         | TD1        | TD0     |

| 0F <sub>HEX</sub> | timer              |       |       |                                                                                             | <timer cour<="" td=""><td>ntdown valu</td><td>Ie&gt;</td><td></td><td></td></timer>       | ntdown valu                                                                        | Ie>                                                       |            |         |

The PCA8565 and PCA2125 oscillators operate over a wider temperature range (up to 125 °C) and are suitable for use in the harsh environments found within automobiles. Power consumption remains low — only 700 nA at 2 V. Serial interface is  $l^2C$  or SPI.

All the RTCs have ESD protection that exceeds 2000 V HBM per JESD22-A114, 200 V MM per JESD22-A115. Charge Device Model values vary from 500 V to 2000 V CDM per JESD22-C101. Refer to the datasheet of the respective device. Latch-up testing, performed in accordance with JEDEC Standard JESD78, exceeds 100 mA.

# 3. Comparison

Table 2 on the next page gives a quick overview of the features, specifications and differences between the RTCs dealt with in this User Manual. The PCF8573 which belongs to the PCF85x3 family is no longer in production and has thus not been included in the table. However, this user manual is useful for this type as well.

Further there are some derived types from the main types listed in the table with small differences in for example delivery form or the number of integrated oscillator capacitors. Consult NXP for more details.

### 3.1 Event counter mode

Two real time clocks, PCF8583 and PCF8593, have an extraordinary feature. It is the event counter mode which can be selected by setting the appropriate bits in the control register. In this mode the oscillator is disabled and the oscillator input is switched to a high impedance state. This mode can be used to count pulses applied to the oscillator input OSCI. There is no crystal in the circuit and OSCO is left open circuit. The event counter stores up to 6 digits of data. Events are stored in BCD format. The 6 digits use three 8 bit registers (hundredth of a second, seconds, and minutes). D5 is the most significant and D0 the least significant digit. Every digit can contain values ranging from 0 to 9 and thus up to 999 999 events can be stored.

It is also possible to set an event counter alarm. When this function is enabled, the alarm occurs when the event counter registers match the programmed value. In this event the alarm flag is set. The inverted value of this flag can be transferred to the interrupt pin by setting the alarm interrupt enable in the alarm control register. In this mode the timer increments once for every one, one hundred, ten thousand or 1 million events, depending on the programmed value of the alarm control register. In all other events, the timer functions are as in clock mode.

Note that immediately following power-on, all internal registers are undefined and must be defined by software. It is also possible that upon power-on the device is initially in event-counter mode in which event the oscillator will not operate until the correct settings are written into the control registers.

The count value will increment on the falling edge. However, after a new count value has been programmed at least one rising edge must have occurred before events will be detected on the falling edge.

#### Table 2. Comparison of six real time clocks

| Features                                                |                                                               | PCx85x                                  | PCx212x family                               |                                         |                                                                |                                         |

|---------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------|----------------------------------------------|-----------------------------------------|----------------------------------------------------------------|-----------------------------------------|

|                                                         | PCF8563                                                       | PCA8565                                 | PCF8583                                      | PCF8593                                 | PCF2123                                                        | PCA2125                                 |

| Unique features                                         | Very low<br>power<br>consumption                              | AEC-Q100<br>automotive<br>qualification | High<br>resolution,<br>RAM, event<br>counter | High<br>resolution,<br>event<br>counter | Extremely<br>low power<br>consumption,<br>electronic<br>tuning | AEC-Q100<br>automotive<br>qualification |

| Type of interface                                       | I <sup>2</sup> C                                              | I <sup>2</sup> C                        | I <sup>2</sup> C                             | I <sup>2</sup> C                        | SPI                                                            | SPI                                     |

| Interface bus speed                                     | 400 kHz                                                       | 400 kHz                                 | 100 kHz                                      | 100 kHz                                 | 7 MHz                                                          | 7 MHz                                   |

| Scratch pad RAM                                         | no                                                            | no                                      | 240 bytes                                    | no                                      | no                                                             | no                                      |

| Year / leap year tracking                               | yes / yes                                                     | yes / yes                               | yes / yes                                    | yes / yes                               | yes / yes                                                      | yes / yes                               |

| Year counter                                            | 2 digit +<br>1 century bit                                    | 2 digit +<br>1 century bit              | 2 bit<br>(4 years)                           | 2 bit<br>(4 years)                      | 2 digit<br>(99 years)                                          | 2 digit<br>(99 years)                   |

| 100 ms, 10 ms time register                             | no                                                            | no                                      | yes                                          | yes                                     | no                                                             | no                                      |

| Electronic tuning register                              | no                                                            | no                                      | no                                           | no                                      | yes                                                            | no                                      |

| Programmable alarm and timer functions                  | yes                                                           | yes                                     | yes                                          | yes                                     | yes                                                            | yes                                     |

| Low voltage detector                                    | yes                                                           | yes                                     | no                                           | no                                      | yes                                                            | no                                      |

| Event counter mode                                      | no                                                            | no                                      | yes                                          | yes                                     | no                                                             | no                                      |

| Option to select between two I <sup>2</sup> C addresses | no                                                            | no                                      | yes                                          | no                                      | no                                                             | no                                      |

| Integrated oscillator capacitor                         | 1 at OSCO                                                     | 1 at OSCO                               | 1 at OSCO                                    | 1 at OSCO                               | 2                                                              | 1 at OSCO                               |

| Supply voltage range                                    | 1.8 V – 5.5 V                                                 | 1.8 V – 5.5 V                           | 2.5 V – 6.0 V                                | 2.5 V – 6.0 V                           | 1.6 V – 5.5 V                                                  | 1.6 V – 5.5 V                           |

| Clock operating voltage                                 | 1.0 V – 5.5 V                                                 | 1.8 V – 5.5 V                           | 1.0 V – 6.0 V                                | 1.0 V – 6.0 V                           | 1.1 V – 5.5 V                                                  | 1.3 V – 5.5 V                           |

| Typical current consumption                             | 250 nA at<br>V <sub>DD</sub> = 1 V                            | 650 nA at<br>V <sub>DD</sub> = 3 V      | 2 µA at<br>V <sub>DD</sub> = 1 V             | 1 μA at<br>V <sub>DD</sub> = 2 V        | 100 nA at<br>V <sub>DD</sub> = 2 V                             | 550 nA at $V_{DD}$ = 3 V                |

| Operating temperature range                             | -40 °C to<br>+85 °C                                           | -40 °C to<br>+125 °C                    | -40 °C to<br>+85 °C                          | -40 °C to<br>+85 °C                     | -40 °C to<br>+85 °C                                            | -40 °C to<br>+125 °C                    |

| AEC-Q100 qualified                                      | no                                                            | Yes<br>(TSSOP8)                         | no                                           | no                                      | no                                                             | yes                                     |

| Packages                                                | U <sup>[1]</sup> , DIP8,<br>SO8,<br>TSSOP8,<br>HVSON10<br>die | TSSOP8,<br>HVSON10                      | U <sup>[1]</sup> , DIP8,<br>SO8,<br>HVQFN20  | DIP8, SO8                               | U <sup>[1]</sup> ,<br>HVQFN16,<br>TSSOP14                      | TSSOP14                                 |

[1] Naked die

Some derived versions are available such as PCF8563A and PCA8565A which include two integrated oscillator capacitors and are also available as naked die.

# 4. Power-on reset (POR)

Traditionally a power-on reset circuit is a circuit that generates a reset pulse once the supply voltage has reached a certain value upon power-up. The purpose is to ensure a defined behavior at start-up. This type of power-on reset is not present in these RTCs.

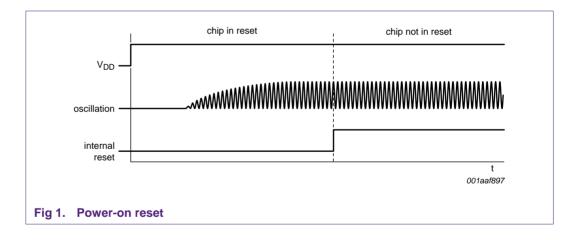

The power-on reset circuit (POR) for these RTCs does not look at the supply voltage, but instead it is based on an internal reset circuit which is active whenever the oscillator is stopped, refer to Fig 1. When power is applied to the device it will take some time for the oscillator to start and during this time the circuit will generate a reset. Also when during operation the OSCI- or OSCO-pin is pulled to ground, causing oscillation to stop, the POR will generate a reset pulse. In the reset state the serial bus logic is initialized and all registers are reset according to the register reset values. Not all registers will be reset. The only registers that are reset are the ones that control a function i.e. decide on clock mode, enable an alarm etc. Refer to the datasheet of the respective device for details.

The power on reset duration is thus directly related to the crystal oscillator start-up time. Due to the long start-up times experienced by these types of circuits on-board testing of the device would take longer too. In order to speed up this, a mechanism has been built in to disable the POR (not for PCF8583, PCF8593 and PCF2123). This is called Power-on reset override. Again, refer to the respective datasheet for details. Once the override mode has been entered, the device stops immediately being reset and set-up operation e.g. entry into the external clock test mode, may commence via the serial interface.

# 5. Voltage-low detector

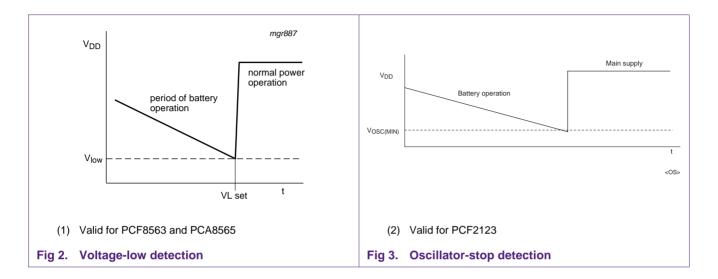

PCF8563, PCA8565 and PCF2123 have an on-chip voltage-low detector, see Fig 2 and Fig 3. When  $V_{DD}$  drops below a certain limit defined as  $V_{low}$ , bit VL in the seconds register of PCF8563 and PCA8565 is set. Generally the VL-bit is intended to indicate that the time might be wrong, not that it necessarely is wrong. It will be set if one of the following four conditions occur:

- The power has just been applied;

- The power has dipped down and then recovered;

- The power has gone away and then come back again;

- When the oscillator stops running.

The implementation in the PCF2123 is slightly different. There a bit OS (Oscillator Stopped) is present instead of VL. The OS flag is set whenever the oscillator is stopped, and therefore also when this is due to the supply voltage dropping too low. The flag can only be cleared by software and only if the oscillator is running again.

In the case of PCF8563/PCA8565 bit VL set indicates that the integrity of the clock information is no longer guaranteed. If the oscillator hasn't stopped, the clock information will still be ok, but with  $V_{DD}$  having dropped below  $V_{low}$  there is no guarantee that this still is the case because there is no way to be sure that the oscillator kept running. The VL flag can only be cleared by software.

Both VL and OS are intended to detect the situation when  $V_{DD}$  is decreasing slowly, for example under battery operation. Should  $V_{DD}$  reach the limit where the flag is set before power is re-asserted, then the flag VL or OS will indicate that time may be (VL) or is (OS) corrupted.  $V_{DD}$  dropping below  $V_{low}$  or  $V_{osc(min)}$  in itself does not cause any register to be reset. Once the oscillator stops some registers will be reset.

# 6. Oscillator

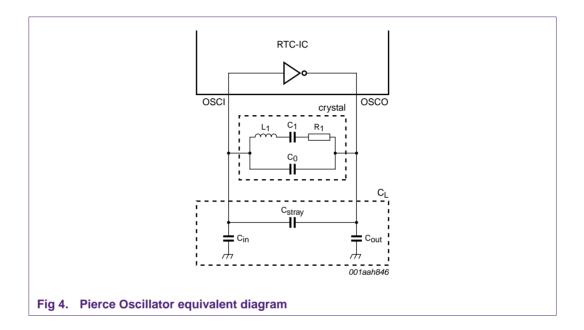

A crystal oscillator as used in a real-time clock, see Fig 4, is built on the principle of Pierce and uses an inverting amplifier with a crystal in the feedback path and load capacitors  $C_{IN}$  and  $C_{OUT}$  to provide the necessary additional phase shift. Some phase shift is contributed as a result of the amplifier's non-zero output impedance in combination with  $C_{OUT}$ . The oscillator operates at the frequency for which the crystal is anti-resonant (i.e. parallel resonant) with the total capacitive load of the oscillating circuit as seen from the pins of the crystal. This total capacitance is called the load capacitance.

The load capacitance is defined as the capacitance seen from the pins of the crystal and is formed by  $C_{IN}$ ,  $C_{OUT}$  and  $C_{STRAY}$  indicated in Fig 4. Electrically the crystal's  $C_0$  is also a load capacitance which affects oscillator characteristics. However, it is not part of the defined 'load capacitance'. During manufacturing the crystal is tuned to the specified frequency with a specified load capacitance connected to the crystal. Since  $C_0$  is part of the crystal, it is automatically taken into account during the adjustment procedure.

$C_{\text{STRAY}}$  is a result of parasitic capacitances due to PCB traces, IC pins etc. and is directly in parallel with  $C_0$  of the crystal. In a practical situation care needs to be taken to keep these parasitic capacitances as low as possible since it will add to the load capacitance and this load capacitance must meet the specified value for the crystal that is being used. If the load capacitance presented to a crystal is smaller than what the crystal was designed for, the oscillation frequency will be too high and thus if used with an RTC, the clock will run too fast.

The inverting amplifier (with feedback resistor, and drive resistor which are not included in Fig 4) is incorporated within the integrated circuit device. On the other hand, the quartz crystal is a discrete device external to the integrated circuit. In the PCF85x3, PCA8565 and PCF2123, PCA2125 the output capacitor  $C_{OUT}$  is integrated on the integrated circuit. PCF8563A, PCA8565A and PCF2123 also include  $C_{IN}$ , see Table 3 for overview.

#### Table 3. Overview of internal and external oscillator capacitors

| Features                                    |           | PCx85     | PCx212x family |           |                     |           |

|---------------------------------------------|-----------|-----------|----------------|-----------|---------------------|-----------|

|                                             | PCF8563   | PCA8565   | PCF8583        | PCF8593   | PCF2123             | PCA2125   |

| Integrated oscillator capacitor             | 1 at OSCO | 1 at OSCO | 1 at OSCO      | 1 at OSCO | 2                   | 1 at OSCO |

| Targeted crystal load capacitance           | 12.5 pF   | 12. 5 pF  | 12.5 pF        | 12. 5 pF  | 7 pF <sup>[1]</sup> | 12.5 pF   |

| Value of integrated C <sub>IN</sub> , typ.  | -         | -         |                |           | 14 pF               | -         |

| Value of integrated C <sub>OUT</sub> , typ. | 25 pF     | 25 pF     | 40 pF          | 25 pF     | 14 pF               | 25 pF     |

| Theoretically required at pin OSCI          | 25 pF     | 25 pF     | 18 pF          | 25 pF     | 0 pF                | 25 pF     |

[1] Can be used with 9 pF and 12.5 pF as well if external capacitance is added

The values used in practice will be a bit smaller than the theoretically required values due to parasitic capacitances present in the application which add to the external physical capacitor.

For the PCF2123 the integrated  $C_{IN}$  and  $C_{OUT}$  are dimensioned for a crystal which requires a load capacitance of 7 pF. If a crystal with required load capacitance of 12.5 pF is used still a small external capacitor is required, otherwise the clock will run too fast. For the other types the input capacitor  $C_{IN}$  is external and needs to be mounted on the printed circuit board. The power consumed by the oscillator circuit is through the amplifier and losses in R<sub>1</sub> of the crystal. Oscillation will start if the loop gain at 360° phase shift is higher than one. The oscillator amplitude increases until the over-all loop gain is reduced to exactly 1 through either non linear effects of the amplifier (self limiting Pierce) or through some form of AGC (Automatic Gain Control) designed in into the amplifier.

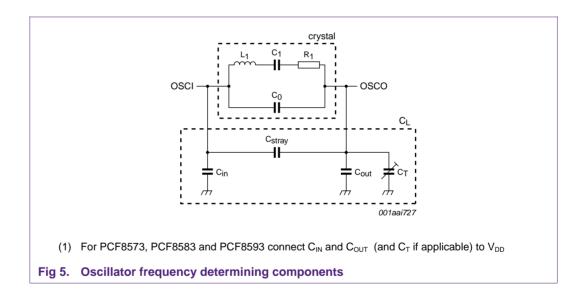

The resonating frequency can be pulled by changing the value of the capacitor at OSCI or by adding a variable capacitor  $C_T$  at OSCO as shown in Fig 5. External capacitors at OSCI and OSCO should be connected to GND, except for PCF8573, PCF8583 and PCF8593. For the latter three it is better to connect these external capacitors to  $V_{DD}$  instead because these devices are manufactured in a process that has the substrate connected to  $V_{DD}$  (n-substrate). In the other RTCs the substrate is at  $V_{SS}$  (p-substrate).

The reactive components indicated in Fig 4 and Fig 5 determine the oscillating frequency. Near the resonance frequency the equivalent circuit of the crystal consists of the motional inductance  $L_1$ , the motional capacitance  $C_1$  and the motional resistance  $R_1$  (in various literature also called series resistance  $R_s$ ). In parallel with this series circuit is the static or shunt capacitance  $C_0$ . It is the sum of the capacitance between the electrodes and the capacitance added by the leads and mounting structure. If one were to measure the reactance of the crystal at a frequency far away from a resonance frequency, it is the reactance of this capacitance that would be measured.

When a crystal is chosen, such a crystal has a specified load capacitance  $C_L$ . During production the crystal manufacturer has adjusted the resonance frequency of the crystal using exactly this capacitance as the load for the crystal. The actual value of  $C_L$  as seen by the crystal in the application is determined by the external circuitry and parasitic

capacitances. The external components of the oscillator have to be chosen such that the actual value of  $C_L$  matches the specified value of  $C_L$ . If there is mismatch the crystal will not run exactly at its specified frequency resulting in the clock running slow or fast.

The crystal manufacturer can manufacture crystals for any load capacitance, but in practice some standard values are used. For use in real-time clocks you may find crystals specified for load capacitances of 7 pF, 9 pF and 12.5 pF with 12.5 pF the most common value.

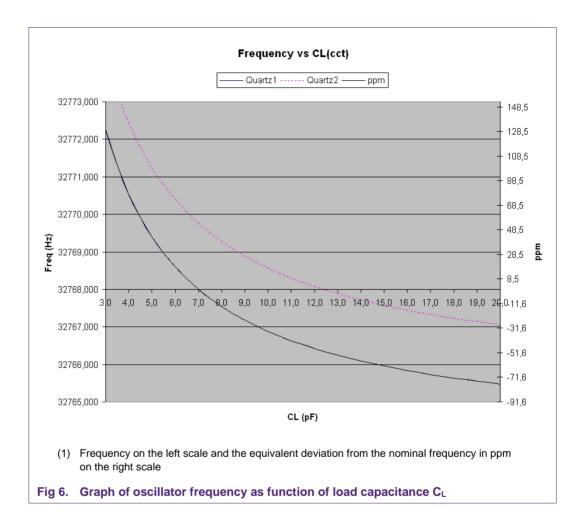

Fig 6 depicts the influence of the load capacitance applied to the crystal on the oscillator frequency. The lower curve represents a crystal with a specified  $C_L$  of 7 pF, the upper curve represents a crystal with a specified  $C_L$  of 12 pF. From this graph it is obvious that the 7 pF crystal is more sensitive to deviations from the specified  $C_L$ . If the applied  $C_L$  is 1 pF lower than specified, the frequency deviation will be 18 ppm, whereas the 12.5 pF crystal will only show a frequency deviation of 6 ppm if the applied  $C_L$  is 1 pF below the specified value. This is not surprising since the same absolute change in load capacitance is a larger relative change if the load capacitance is smaller. A lower load capacitance however will result in lower power consumption and in cases where this is an important requirement a crystal with lower required  $C_L$  could be selected.

UM10301

Now in order to determine the value of  $C_L$  resulting from  $C_{IN}$ ,  $C_{OUT}$  (plus  $C_T$  if mounted) and  $C_{STRAY}$  it is necessary to realize that seen from the crystal,  $C_{IN}$  and  $C_{OUT}$  are effectively in series; the 32 kHz signal goes from OSCI through  $C_{IN}$  to ground, via ground to  $C_{OUT}$  and then through  $C_{OUT}$  to OSCO. In parallel with this series circuit is  $C_{STRAY}$ . For the remainder of this discussion, whenever in formulas  $C_{OUT}$  is written this represents either the value of  $C_{OUT}$  only, or in case a trimming capacitor  $C_T$  is present too, the sum of  $C_{OUT}$  and  $C_T$ . Now the load capacitance  $C_L$  is given by:

$$C_{L} = \frac{C_{IN} \cdot C_{OUT}}{C_{IN} + C_{OUT}} + C_{STRAY}$$

Since  $C_0$  is in parallel with  $C_L$  the total capacitance in parallel with the motional arm  $L_1\mathchar`-C_1\mathchar`-R_1$  is given by

$$C_{PAR} = \frac{C_{IN} \cdot C_{OUT}}{C_{IN} + C_{OUT}} + C_{STRAY} + C_0$$

The motional arm is a series circuit, which forms a closed circuit because there is a capacitance  $C_{PAR}$  connected in parallel to this series circuit. Of course the crystal itself can't oscillate stand alone, but the equivalent capacitance C which determines together with L<sub>1</sub> the resulting resonance frequency is now given by the series circuit of  $C_{PAR}$  and  $C_1$ . Thus C is given by

$$C = \frac{C_{1} \cdot \left\{ \frac{C_{IN} \cdot C_{OUT}}{C_{IN} + C_{OUT}} + C_{STRAY} + C_{0} \right\}}{C_{1} + \left\{ \frac{C_{IN} \cdot C_{OUT}}{C_{IN} + C_{OUT}} + C_{STRAY} + C_{0} \right\}}$$

Typical values for crystal parameters are given in Table 4. From these values it is clear that  $C_1$  is several orders of magnitudes smaller than the other capacitances in this expression and therefore  $C_1$  dominates. C will be in the order of magnitude of  $C_1$  but it will be a bit smaller as a result of  $C_{PAR}$  in series.

With  $\omega = \frac{1}{\sqrt{LC}}$  and  $Q = \frac{1}{\omega C} \cdot \frac{1}{R_1}$  the resulting resonance frequency and quality

factor can be calculated.

Because  $C_1$  is orders of magnitude smaller than the other capacitances Q can be approximated by

$$Q_a = \frac{1}{\omega C_1} \cdot \frac{1}{R_1}$$

Taking the numbers from Table 4 yields for  $L_1$  and Q:

$$L_{1} = \frac{1}{(2\pi \cdot f_{0})^{2} \cdot C_{1}} = \frac{1}{(2\pi \cdot 32768)^{2} \cdot 2.1 \cdot 10^{-15}} = 11234 H$$

$$Q = \frac{1}{(2\pi \cdot f_{0}) \cdot C_{1} \cdot R_{1}} = \frac{1}{(2\pi \cdot 32768) \cdot 2.1 \cdot 10^{-15} \cdot 55 \cdot 10^{3}} = 42053$$

This L of around 11000 H resulting in a Q of around 42000 explains why starting up the oscillator as well as stopping it can easily take more than a second. An oscillating quartz crystal is actually a mechanical oscillation and starting or stopping this takes time. Calculations of start up time and more in-depth theory about the oscillator and load capacitance are beyond the scope of this user manual, but can be found in AN10716 "Background information and theory related to Real Time Clocks and crystals".

The use of AGC's improve start up by high drive initially to get it going and then reduce drive for low power.

| Parameter                  | Value       | Unit                  | Source |

|----------------------------|-------------|-----------------------|--------|

| f <sub>0</sub>             | 32768       | Hz                    | [2]    |

| $\Delta f / f_0$           | ±100        | ppm                   | [2]    |

| Aging; $\Delta f \ / f_0$  | ±3±5        | ppm                   | [2]    |

| B, freq(T)                 | -0.035      | ppm / °C <sup>2</sup> | [2]    |

| C <sub>1</sub>             | 2.1         | fF                    | [2]    |

| C <sub>0</sub>             | 1.21.5      | pF                    | [2]    |

| C <sub>IN</sub>            | 25 ± 10     | pF                    | [1]    |

| C <sub>IN</sub> , temp co. | +47         | ppm/°C                | [1]    |

| R <sub>1</sub>             | 5080        | kΩ                    | [2]    |

| $C_{T}$ variable           | 425         | pF                    | [3]    |

| $C_{T}$ , temp co.         | 300         | ppm/°C                | [3]    |

| $C_{T}$ fixed 0603         | Any         | pF                    | [4]    |

| $C_{T}$ fixed, tc          | ±30 for C0G | ppm/°C                | [4]    |

Table 4.

Typical values for crystal and surrounding capacitors

Sources for values in table 4:

- [1] NXP, Datasheet PCF8563, February 2008.

- [2] Product Data Sheets, MicroCrystal.

- [3] Murata TZB04 trim capacitor

- [4] Vishay Beyschlag, datasheet ceramic multilayer capacitor, C0G

# 6.1 Oscillation allowance

Fig 4 shows the Pierce oscillator schematic with the external crystal. For an oscillation to take place the real component of the oscillator impedance has to be larger than the motional resistance  $R_1$  (sometimes called  $R_S$  or ESR). If  $R_1$  is too large no oscillation will take place since no operating point can be reached.

Similarly, if the supply voltage is too low or the temperature is too low, no oscillation can build up.

A method to test how much margin the design has is to include a resistor  $R_x$  in series with the crystal. The value of the resistor is changed (a trimmer is useful here) to see at which values of  $R_x$  oscillation starts and stops. Starting from a large value of  $R_x$  the resistance is lowered until oscillation starts. This value of  $R_x$  is called  $R_{x-start}$ . Now the value is increased again until oscillation stops,  $R_x$  is called  $R_{x-stop}$ .

The oscillation allowance OA is defined as:

$$OA = R_{X-start} + R_1$$

As a rule of thumb, the motional resistance of the crystal chosen should be

$$R_1 \le \frac{OA}{5}$$

This test can be done in the lab under room temperature. This should give enough safety margins to allow for production spread of IC and crystal and to deal with the increasing value of  $R_1$  under influence of increased temperature.

## 6.2 Using an external oscillator

It is possible to supply a clock signal from an external oscillator instead of using the internal oscillator if for some reason it is desired to not use the internal oscillator. In this case no crystal will be connected to the OSCI and OSCO pins. Instead the external oscillator must be connected to OSCI while OSCO must be left floating.

The signal may swing from V<sub>SS</sub> to V<sub>DD</sub>. However, with a crystal attached the signal amplitude at the oscillator input pin would be about 500 mV, swinging around a 250 mV bias i.e. never going negative (not for PCF8583 and PCF8593, see below). For the PCF85x3 supplying a signal with amplitude between 500 mV and 1000 mV is a good starting point, with the bias such that the signal doesn't go negative and operates in the same region as would have been the case with a crystal. Square or sine wave is both ok. For the PCF2123 the amplitude should be somewhat smaller. If the oscillator amplitude is larger than the supply voltage to the RTC it is advisable to use a resistive divider for the oscillator signal to bring its amplitude within the supply voltage of the RTC. Without such a divider it will work too and nothing will be damaged (as long as the currents via the clamping diodes don't exceed the maximum limits) because the device has internal clamping diodes from V<sub>SS</sub> to OSCI and from OSCI to V<sub>DD</sub> (not on PCF2123). However, performance will be better if the oscillator amplitude is brought within the range from 0 V to the actual V<sub>DD</sub> used for the RTC. This will first prevent periodic currents flowing via the upper clamping diode to the decoupling capacitor on the supply pin. Secondly the signal

levels can be tuned such that they are similar to those when the internal oscillator is used.

Suppose that the RTC is supplied with 3.3 V and that the amplitude of the external CLK is 5 V (from 0 V to 5 V). Using 1 M and 220 k resistors the signal could be reduced to  $(220 / 1220) \times 5 V = 0.9 V$ . This is better in line with the signals that the internal circuitry handles when an external crystal is used as is the case in the standard application. This reduced signal can then be applied to the OSCI pin directly or via a small capacitor of e.g. 22 pF - 100 pF. This is a lower power option, where bias from the resistive devider and oscillator will be lost and will be determined by the oscillator input. This option is also more susceptible to noise.

If PCF8583 and PCF8593 are used together with a crystal, the signal would swing around a bias of some 100 mV below  $V_{DD}$ . If these RTCs are fed with an external signal, it should be either AC coupled, or swinging with amplitude of around 1 V below  $V_{DD}$ , where the lower value may be lower than 1 V below  $V_{DD}$  as well. For example, swinging from ( $V_{DD} - 1$  V) to  $V_{DD}$  would be ok, but also swinging from  $V_{SS}$  to  $V_{DD}$ .

**Remark**: Values mentioned here are guidelines only. For every application correct operation must be verified.

# 7. Crystal and crystal selection

Select a crystal of the tuning fork type with a nominal frequency of  $2^{15}$  Hz = 32768 Hz. The allowed tolerance depends on the requirements for the application and on whether a trimming capacitor will be used. If a trimming capacitor will be used even a tolerance of ±100 ppm is ok since it can be compensated. Either through hole or surface mount crystals can be used where the latter provide the smallest dimensions which makes the circuit less susceptible to noise pick up.

As previously pointed out crystals used for RTCs come in three versions, optimized for three standard values for  $C_L$  with 12.5 pF the most common. Generally, an RTC using a 12.5 pF crystal has a timekeeping current of about 1.6x more than an RTC using a 7 pF crystal. If lowest power consumption is a key consideration, a 7 pF crystal (some manufacturers use 6 pF) should be selected. The PCF2123 has been optimized for use with such a crystal. The other RTCs include load capacitance optimized for a 12.5 pF crystal. Using a 7 pF crystal would require an external capacitor of about 9.7 pF and thus the capacitances at OSCI and OSCO would not be balanced. In general this may have a detrimental influence on start-up behaviour but no problems are expected when a 7 pF crystal is used in combination with the PCF8563 because it uses an AGC in its oscillator.

An oscillator using a 12.5 pF crystal will be more stable and less susceptible to noise and parasitic capacitances. One reason for this is that the capacitors on the input and output will have higher values and therefore create a higher load for noise. Further these higher values make the parasitic capacitance relatively smaller for the same PCB.

Besides technical considerations there are also procurement issues. Crystals designed for a 12.5 pF load capacitance are readily available through many distributors. Crystals designed for a load capacitance of 7 pF or 9 pF are not as readily available and may have longer lead times or require a minimum quantity to be purchased.

The series resistance  $R_1$  should ideally remain below 50 k $\Omega$ . If higher values are used (up to 100 k $\Omega$  is ok) the current consumption of the oscillator will increase a bit. If the

value is really too high start up problems may occur, but up to  $100 \text{ k}\Omega$  no start up problems are expected. See 6.1"Oscillation allowance".

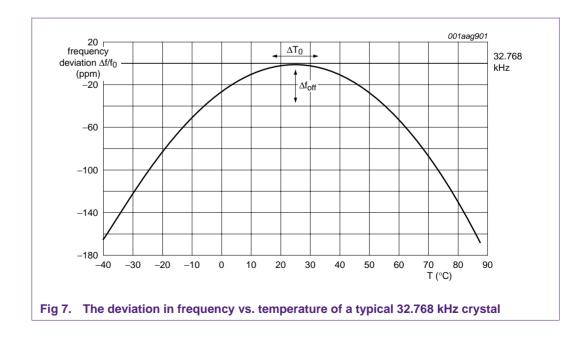

The frequency accuracy of the oscillator depends mainly on the accuracy of the crystal and on how well the crystal is matched to the oscillator capacitive load ( $C_L$ ). A too small capacitive load results in the oscillator running fast, if the capacitive load is greater than what the crystal was designed for the oscillator and thus clock runs slow. This initial error is indicated in Fig 7 as  $\Delta f_{off}$ . The largest influence on accuracy is a result of the temperature dependence of the crystal.

# 7.1 Modes which don't work

To keep time with an adequate accuracy it is necessary to use a quartz crystal and thus the use of a quartz crystal is always assumed in this application note. A very low power crystal oscillator as used in an RTC requires a different set of parameters compared to a universal oscillator accepting crystals, RC- and LC networks or a ceramic resonator. The oscillator circuit is not designed for operating with RC or LC networks neither for use with a ceramic resonator. Ceramic resonators have a much shorter start up time than crystals, about 100 times faster. However, they have lower frequency accuracy (initial tolerance, temperature variations, drift) and since in an RTC accurate timekeeping is the goal, ceramic resonators are not a good choice for an RTC. Use a crystal.

### 7.2 Effect of temperature

A tuning fork crystal is usually cut such that its frequency over temperature is a parabolic curve centered around 25 °C, see Fig 7. This means that a tuning fork crystal oscillator will resonate close to its target frequency at room temperature, but will slow down when the temperature either increases or decreases from room temperature.

The frequency of a typical crystal at a specific temperature T is given by:

$$f = f_0 \Big[ 1 + B \big( T - T_0 \big)^2 \Big]$$

Further f<sub>0</sub> can be considered to consist of two components as

$$f_0 = f_{nom} + f_{off}$$

Here  $f_{nom}$  is the nominal frequency as specified and  $f_{off}$  the offset from this nominal frequency which is a result of production spread, both at room temperature.

$$f = \left(f_{nom} + f_{off}\right) \cdot \left[1 + B(T - T_0)^2\right]$$

For the frequency deviation  $\frac{\Delta y}{f_{nom}} = \frac{f - f_{nom}}{f_{nom}}$  and expressed in ppm, this results in:

$$\frac{\Delta f}{f_{nom}} = \left\{ B (T - T_0)^2 + \frac{f_{off}}{f_{nom}} \left[ 1 + B (T - T_0)^2 \right] \right\} \cdot 10^6$$

(7.1)

In these equations f is the frequency,  $f_0$  is the frequency at room temperature, B is the parabolic coefficient, T is the temperature and  $T_0$  is the turnover temperature where the apex of the drift versus temperature curve occurs.

Three variables in equation (7.1) influence the frequency as a function of temperature. These are the parabolic coefficient B, the turnover temperature  $T_0$  and the room temperature offset  $f_{off}$ . The crystal manufacturer specifies these parameters and typical values are  $B = -0.035 \text{ ppm/°C}^2$  to  $-0.04 \text{ ppm/°C}^2$ ,  $T_0 = 25 \text{ °C}$ ,  $\Delta T_0 = \pm 5 \text{ °C}$  and  $f_{off} = 30 \text{ ppm}$ . The coefficient B has a very small spread for various crystals of one type, but it has the largest effect on the parabolic nature of the frequency deviation as a function of temperature. Variation in the turnover temperature  $T_0$  will shift the deviation curve left or right, variation in the offset at room temperature will shift it up or down. In practice the combination of variation in  $T_0$  and offset at room temperature easily results in a (lack of) accuracy of  $\pm 30$  ppm at room temperature which equates to a time deviation of around 15 minutes per year.

Application note AN10652 "Improved timekeeping accuracy with PCF8563 using external temperature sensor" describes how accuracy over temperature can be improved using an external temperature sensor and a software algorithm. It can be used for the other RTCs in this manual too in conjuction with the respective datasheets.

PCF2123 contains an offset register which allows fine tuning of the clock. This can be used to compensate for crystal aging and temperature variations. See section 10.1.

Automotive RTCs PCA8565 and PCA2125 operate also at high ambient temperatures of 125 °C. Obviously also the crystal selected for these applications should be able to

handle this temperature. Generally metal can quartzes are not recommended for high temperatures because the termal cycling (expansion of package) will cause leakages in the hermetically sealed package. Micro Crystal of Switzerland manufactures a wide range of crystals which include crystals designed to operate up to 125 °C.

# 8. Capacitors and capacitor selection

The influence of temperature on the accuracy of the RTC application due to the temperature coefficient of the capacitances  $C_{IN}$  and  $C_{OUT}$  is far less than due to the temperature coefficient of the crystal. Nevertheless it is good to be aware of some differences between the various types of capacitors (dielectric) around.

Ceramic capacitors tend to have low inductance because of their flat plate construction. Most other types of capacitor are wound and thus inductive. Nowadays SMD capacitors are dominant in small signal applications.

The EIA (Electronic Industries Alliance) has issued EIA-535 which defines capacitor dielectric classes. Class I and Class II dielectrics have been defined. Within these classes several types of dielectric exist. The most common ceramic types are C0G/NP0, X7R, Y5V and Z5U but others exist too.

COG (EIA) or NP0 is the highest quality of these with the lowest capacitance / temperature dependence (Negative-Positive Zero), but has a lower permittivity, which means that its capacitance range is more restricted. NP0 refers to the shape of the capacitor's temperature graph and for NP0 this graph is nearly flat. It also exhibits a negligible capacitance and dissipation factor change with voltage or frequency.

X7R is a reasonably stable high-permittivity dielectric which allows capacitance values up to 1µF into a reasonable package. The available range is in the order from 100 pF to 22 µF in SMT, larger values are available in leaded packages. X7R formulations fall into EIA Class II materials. X7R is the most popular of these intermediate dielectric constant materials. Its capacitance variation as a function of temperature is within ±15 % from -55 °C to +125 °C. This capacitance change is non-linear and therefore difficult to express in ppm/°C since it changes over the temperature range. Capacitance for X7R varies under the influence of electrical operating conditions such as voltage and frequency. This rules out many applications, leaving only the general purpose applications like coupling and decoupling. The leakage current is sufficiently low.

Y5V formulations are for general-purpose use in a limited temperature range. Available range is from 1 nF to 22  $\mu$ F in SMT, larger in leaded packages. They have a wide capacitance change of +22 % to -82 % over the operating temperature range of -30°C to +85°C. As an example, at 31% of the rated voltage (5 V over a 16 V capacitor) the resulting capacitance will have reduced to a quarter of the rated value. The effective decoupling capacitance present may thus be much less than expected. Y5V's high dielectric constant allows the manufacture of the highest capacitance value in a given case size. These characteristics make Y5V ideal for decoupling applications within limited temperature range. When specifying the values, the dependence on temperature and applied voltage must be taken into account.

Z5U shows in comparison to the previous types a much worse performance. Its capacitance changes by over 50 % with changes in temperature and applied voltage. Its temperature range is only +10 °C to +85 °C. Its initial tolerance can be as high as -20 %

to +80 %. Its only redeeming feature is its high permittivity which allows high capacitance values, typically ranging from 1 nF to 4.7  $\mu$ F. Good for bypass and coupling applications. It has low price, small size and low temperature stability.

<u>Conclusion</u>: For the oscillator only C0G types should be used. This will almost always automatically be the case since the other types are usually not available in such small values. For the decoupling of the RTC, use a capacitor with X7R dielectric. Using SMD packages results in the lowest parasitic inductances and the small dimensions enable the smallest loops which reduces sensitivity to EMI.

A more expensive alternative for the decoupling X7R capacitor is a film capacitor using Polyethylene naphthalate (PEN), another form of polyester. It has very good heat resistance, but is otherwise much like polyester. It is available in larger sizes than COG ceramic, lower temperature drift than polyester, and lower leakage than X7R. PEN capacitors are available to 125 °C. It is commonly found in SMD capacitors, including large values (>1  $\mu$ F).

# 9. Accuracy

How accurate is accurate??

The international System of Units (SI) has defined the second as the duration of 9,192,631,770 cycles of radiation corresponding to the transition between two energy levels of the ground state of the cesium-133 atom. This definition makes the cesium oscillator (often called an atomic clock) the primary standard for time and frequency measurements. Its accuracy is extremely high with deviations of only a second per several million years. This equates to accuracy in the order of 10<sup>-8</sup> ppm or better.

In dealing with RTCs it is common to express accuracy in ppm, parts per million. But what does it mean in more human units? A clock going too fast 1 s/day has an accuracy of 1 / (number of seconds in a day) = 1 / ( $24 \times 3600$ ) = 11.57 ppm. The other way around, 20 ppm is about 1 minute per month.

1 s/week = 1.65 ppm, 1 s/month = 0.4 ppm and 1 s/year = 0.031 ppm. In contrast, a good mechanical watch has a deviation of less than 12 s/day or 1300 ppm.

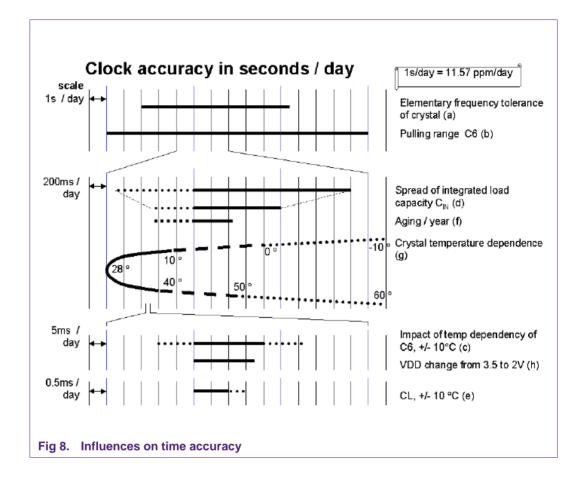

Fig 8 compares the magnitude of the different spreads and variations.

The RTC accuracy dominantly depends on the parameters of the resonating crystal. The initial frequency tolerance  $f_{off}$  can be compensated by tuning the external capacitance. The temperature coefficient of the external capacitances has almost no effect. The main contribution comes from the temperature coefficient of the crystal. In contrast to AT-cut crystals tuning fork crystals have the parabolic temperature dependence indicated in Fig 7 which results in a slow down of the clock if the temperature is lower or higher than  $T_0$  which is in the range of 25 to 28 degrees. The same type of crystal is also used in wrist watches and the turnover temperature of the crystal matches well with the temperature at the wrist which is typically about 28 °C and quite stable.

The various influences indicated in Fig 8 are described below:

- The line at the top indicates the frequency tolerance of the crystal in this example. The distance between two vertical lines represents (at the top) 1 s/day or 11.57 ppm. The crystal spread covers about 8.5 lines and thus indicates a spread of about 100 ppm.

- 2. The production spread of the crystal can be compensated by adjusting the pulling capacitor  $C_T$  (in the graph called  $C_6$ ) as long as the value of  $C_T$  is chosen correctly. Here the pulling range is large enough to compensate for a spread of ±175 ppm. Typically a variable capacitor has a temperature coefficient of ±300 ppm/°C to 500 ppm/°C. This capacity change has a very small influence on the accuracy of the oscillator and its influence is shown in the third line from the bottom of the graph. The solid line shows the impact of  $C_T$  (here  $C_6$ ) if the value is small. If  $C_T$  is large the variation is larger as indicated with the dotted line.

- 3. Zooming in on a range of about 35 ppm...

- 4. The integrated load capacitance has a finite production spread and its potential influence on the accuracy of the oscillator depends on the value of the integrated capacitor. Whether the internal capacitor is connected to the input ( $C_{IN}$  or to the output  $C_{OUT}$ ) doesn't make a difference. The solid line (third solid line from the top) covers a range of 1.8 s/day, or around 21 ppm. A greater value of  $C_{IN}$  could have a larger influence indicated by the dotted line.

- Tuning C<sub>T</sub> will increase the initial accuracy, indicated by reducing the range covered to the spread of C<sub>IN</sub>. Depending on how well C<sub>T</sub> is tuned, the initial spread can be well compensated for.

- 6. Here the influence on accuracy due to aging of the crystal is given. This shift occurs mainly during the first year of the crystal's life and in the graph a range of about 420 ms/day to 850 ms/day is indicated (±10 ppm). So if the RTC were running correctly initially, after a year it could be fast or slow by about 0.4 s/day.

- 7. As already mentioned and illustrated in Fig 7, the largest impact on the accuracy is due to the temperature dependence of the crystal. The parabolic nature of this dependence is indicated here as well and covers about 40 ppm over the temperature range -10 °C to +60 °C.

- 8. The impact of a change in  $V_{DD}$  is small; a  $\Delta V_{DD}$  of 1.5 V will change the clock speed by about 17 ms/day.

From this an important recommendation follows: If possible place the crystal and ICcircuit at the spot with the least temperature variations.

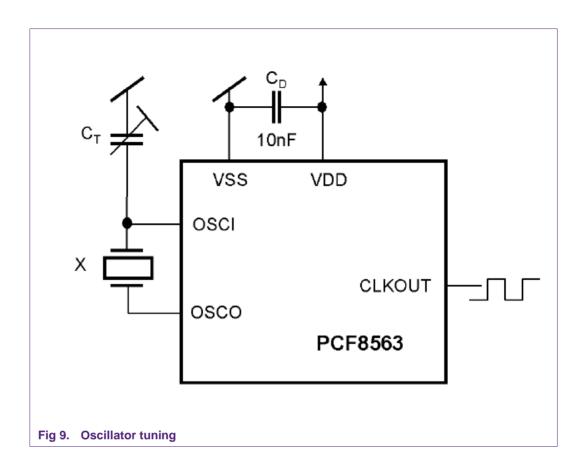

# 10. Oscillator tuning

The PCF8563, PCF2123, PCA8565 and PCA2125 all have a CLKOUT pin which is an open drain output. It provides the option to output the buffered crystal frequency (or a lower frequency derived from the crystal frequency using division by a power of 2) which can be achieved by enabling CLKOUT in the appropriate control register and choosing the desired frequency. Refer to the datasheet of the actual device used for details on how to enable CLKOUT and set the frequency at this pin. Possible output frequencies for the PCF8563 and PCA8565 are 1 Hz, 32 Hz, 1024 Hz and 32768 Hz. The PCF2123 and PCA2125 offer some additional choices and the possible frequencies at the CLKOUT pin are 1 Hz, 1024 Hz, 2048 Hz, 4096 Hz, 8192 Hz, 16384 Hz and 32768 Hz.

PCF8573, PCF8583 and PCF8593 do not include a CLKOUT pin.

Having the CLKOUT pin enables easy tuning of the crystal frequency. A designers' initial impulse may be to connect an oscilloscope probe to the OSCO pin, but this is not a good idea. It may cause the oscillator to stop, but even if the oscillator keeps running the added capacitance of the probe will cause a drift in oscillator frequency. By connecting a pull-up resistor to the CLKOUT pin and measuring the frequency there, a much more accurate result can be achieved. The frequency can now be tuned by adjusting the variable capacitor  $C_T$ .

Remark: Touching the adjustment screw often causes the capacitance to shift. The setup is shown in Fig 9.

Accuracy:

In order to be able to adjust the clock with accuracy better than 1 s/day, the frequency counter used to check the output at CLKOUT should have at least an 8 digit reading with an accuracy of 1 ppm.

Given a nominal frequency of 32.768 kHz, 1 ppm = 32.728 mHz (milli Hertz). Therefore +1 ppm = 32768.0327 Hz, -1 ppm = 32767.9673 Hz. Tune the oscillator while it is at the average operating temperature of the application.

The PCF8573 can be tuned by monitoring the 128 Hz signal at the FSET output.

Tuning the PCF8583/93 is somewhat more difficult since no buffered clock signal is available. There are four different options, all with their own drawbacks:

- Measure the period of the 1 s output signal (countdown timer). This however is time consuming;

- Attach the frequency counter probe to the OSCO-pin. This adds capacity to the OSCO-pin and detunes (lowers) the oscillator frequency by Δf. The frequency adjustment now needs to be lower by the same Δf in order for the clock to run at the correct speed after the probe has been removed again. Obviously the difficulty here lies in determining how big Δf is;

- In the watch industry the frequency is coupled out acoustically. A sensitive microphone is placed near the crystal. The signal is then fed as input to the tuning gear.

- In the datasheets of PCF8583 and PCF8593 the following method is described: Using the alarm function (via the l<sup>2</sup>C-bus) a signal faster than 1 Hz can be generated at the interrupt output for fast setting of a trimmer. Procedure:

- Power-on;

- Initialization (alarm functions).

Routine:

- Set clock to time T and set alarm to time T +  $\Delta$ T

- At time  $(T + \Delta T)$  (Interrupt) repeat the routine.

However, this only works well when  $\Delta T$  is an integer number of seconds. The 1/10 s and the 1/100 s are derived from a combination of 1 Hz, 2 Hz, 4 Hz, 8 Hz, 16 Hz, 32 Hz etc. signals. The accuracy is therefore only < ± 5 ms. Generating an alarm after T +  $\Delta T$  with  $\Delta T$  = 20 ms will show a jitter of plus or minus 5 ms which makes automatic tuning very complicated.

### 10.1 PCF2123 Offset register

The PCF2123 incorporates an offset register which can be used to implement several functions, e.g.:

- Ageing adjustment

- Temperature compensation

- Accuracy tuning

The offset is made once every two hours in the normal mode, or once every hour in the course mode. Each LSB will introduce an offset of 2.17 ppm for normal mode and 4.34 ppm for course mode. These values are based on a nominal 32.768 kHz clock. The offset value is coded in two's complement giving a range of +63 LSB's to -64 LSB's. The correction is made by adding or subtracting 64 Hz clock correction pulses, thereby changing the period of a single second.

In normal mode, the correction is triggered once every two hours and then correction pulses are applied once per minuted until the programmed correction value has been implemented.

In course mode, the correction is triggered once per hour and then correction pulses are applied once per minute up to a maximum of 60. When absolute correction values of greater than 60 are used, additional correction pulses are made in the 59<sup>th</sup> minute.

It is possible to monitor when correction pulses are applied. The correction interrupt enable (CIE) mode will generate a 1/128 second pulse on INT for every correction applied. In the case where multiple correction pulses are applied, a 1/128 second interrupt pulse will be generated for each correction pulse applied. Correction is applied to the 1 Hz clock. Any timer or clock output using a frequency of 1 Hz or below will also be affected by the correction pulses. For more details, refer to the PCF2123 datasheet.

# 11. Century and leap year, Daylight Saving Time

For details on how to implement century tracking and year / leap year tracking, please refer to the datasheets of the respective RTC since register set up differs from type to type. The product comparison in Table 2 shows which parts include century, year and leap year tracking.

## **11.1 Century tracking**

The PCF8563 and PCA8565 contain an 8-bit year register which holds the current year coded in BCD format. These two RTCs further contain a century flag which is toggled when the year counter proceeds from 99 to 00.

PCF8583 and PCF8593 have a four year calendar only and no provision to deal with century change. Also the PCF8573 has no provision to deal with century change.

PCF2123 and PCA2125 contain an 8-bit year register which holds the current year coded in BCD format. There is no century flag. Therefore application firmware needs to deal with century change.

# 11.2 Year and leap year tracking

A leap year (or intercalary year) is a year containing one extra day in order to keep the calendar year synchronised with the astronomical or seasonal year. Adding an extra day to the calendar every four years compensates for the fact that a solar year is *almost* six hours longer than 365 days. However, the duration of a solar year is slightly less than 365.25 days and therefore some exceptions to this rule are required. Years that are evenly divisible by 100 are not leap years unless they are also evenly divisible by 400. For example, 1600 and 2000 were leap years, but 2100, 2200 and 2300 will not be.

The PCF8563, PCA8565, PCF2123 and PCA2125 all contain an 8-bit year register which can hold values from 00 to 99 in BCD format. These real time clocks compensate for leap years by adding a 29<sup>th</sup> day to February if the year counter contains a value which is exactly divisible by 4, including the year 00. Therefore in the year 2100 these RTCs add one day to February, where they shouldn't because it is not a leap year. Until then however leap year correction is correct and automatic.

PCF8583 and PCF8593 have a four year calendar only, which includes leap year tracking. The application firmware needs to deal with keeping track of the actual year.

The PCF8573 has a time counter which counts minutes, hours, days, and months, however, no years. It provides a calendar function in which firmware needs to track the years and which needs to be corrected once every four years to allow for leap year.

# 11.3 Daylight Saving Time (DST)

There is no provision to deal with day light saving time. Since DST is not implemented equally worldwide and can change often, it is usually better not to implement DST in the RTC but to have the application firmware deal with it. Therefore customers whose applications depend on proper adjustment to DST are advised to design their products such that firmware handles DST changes.

# 12. Initialization and setting of alarm and timer

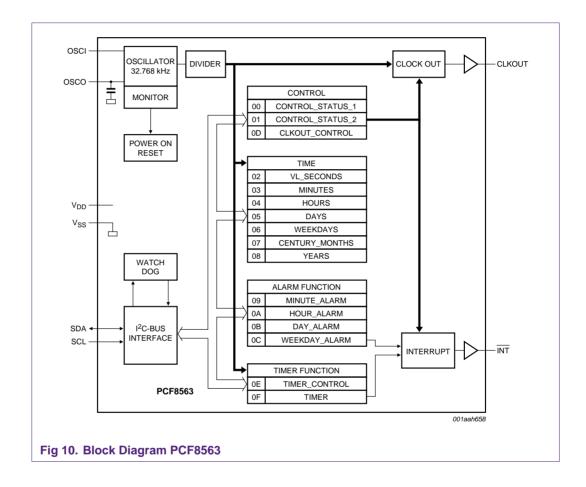

Setting the clock is a straightforward procedure, setting first the mode and then the actual time. This example is for the PCF8563 and for reference its block diagram is given in Fig 10 which shows the registers and their addresses. The procedure for the other RTCs is similar but there are small differences in register structure and therefore the appropriate datasheet should be consulted first.

Examples for initialisation and setting of time, alarm and timer are given below.

## **12.1** Initialization of the RTC and setting the time

Table 5 on the next page shows the sequence of commands to be sent to the RTC for initialization and setting the time.

In this example the time to be set is Friday, July 16 2008, 2:45 pm.

| Sequence of commands / data to be sent |     |                     |                                                      |  |  |

|----------------------------------------|-----|---------------------|------------------------------------------------------|--|--|

| Binary (BCD)                           | HEX | Register<br>Address | Comments                                             |  |  |

|                                        |     |                     | generate I <sup>2</sup> C start condition            |  |  |

| 1010 0010                              | A2  |                     | I <sup>2</sup> C slave address, write                |  |  |

| 0000 0000                              | 00  |                     | word address 0, next bytes are data                  |  |  |

| 0000 0000                              | 00  | 00                  | control/status 1, no test modes or POR override      |  |  |

| 0000 0000                              | 00  | 01                  | control/status 2, no alarm/timer flags or interrupts |  |  |

| 0000 0000                              | 00  | 02                  | set seconds, clear voltage low detector              |  |  |

| 0100 0101                              | 45  | 03                  | set minutes to 45                                    |  |  |

| 0001 0100                              | 14  | 04                  | set hours to 14                                      |  |  |

| 0001 0110                              | 16  | 05                  | set days to 16                                       |  |  |

| 0000 0101                              | 05  | 06                  | set weekdays to Friday, Monday is day 1              |  |  |

| 1000 0111                              | 87  | 07                  | set month to 7 and century bit to 1                  |  |  |

| 0000 1000                              | 08  | 08                  | set years to 08                                      |  |  |

| 1000 0000                              | 80  | 09                  | disable minute alarm and reset to 00                 |  |  |

| 1000 0000                              | 80  | 0A                  | disable hour alarm and reset to 00                   |  |  |

| 1000 0000                              | 80  | 0B                  | disable day alarm and reset to 00                    |  |  |

| 1000 0000                              | 80  | 0C                  | disable weekday alarm and reset to 00                |  |  |

| 1000 0000                              | 80  | 0D                  | set frequency out to 32768 Hz e.g. for tuning        |  |  |

| 0000 0000                              | 00  | 0E                  | timer switched off                                   |  |  |

|                                        |     |                     | generate I <sup>2</sup> C stop condition             |  |  |

# Table 5.Setting the time and date

### 12.2 Alarm

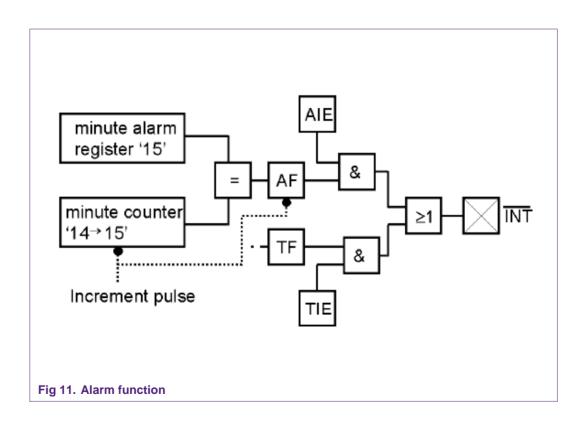

It is possible to program several types of alarm. Let's take the example to set an alarm such that always 15 minutes past the hour the alarm flag AF is set and an interrupt generated.

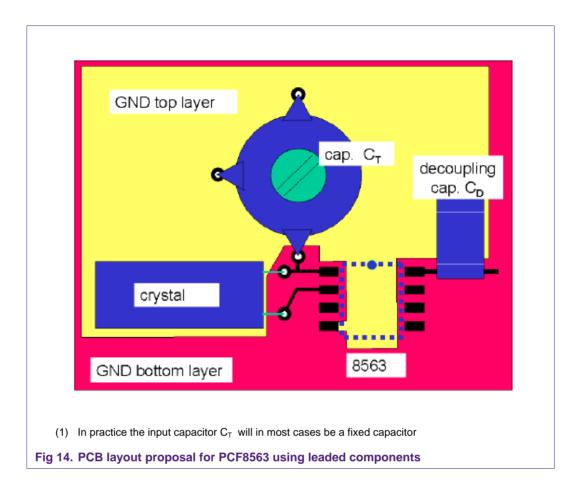

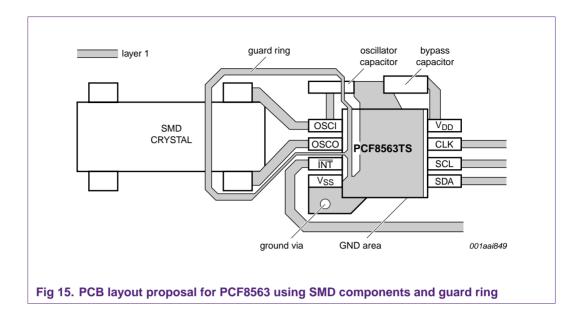

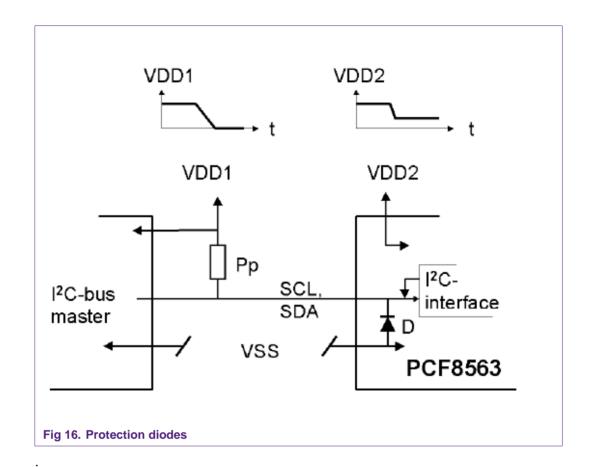

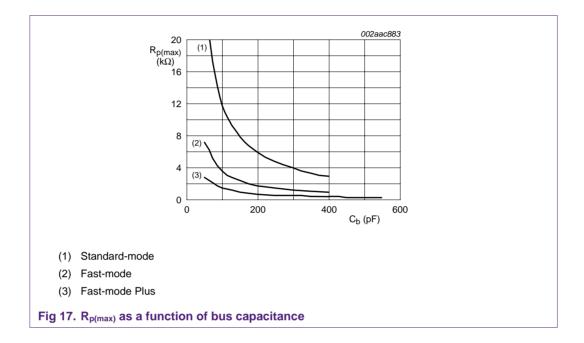

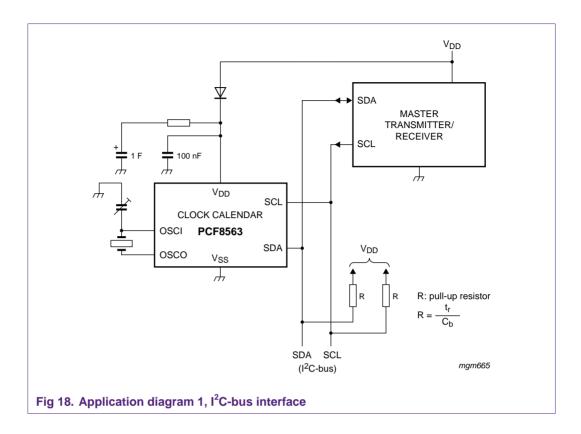

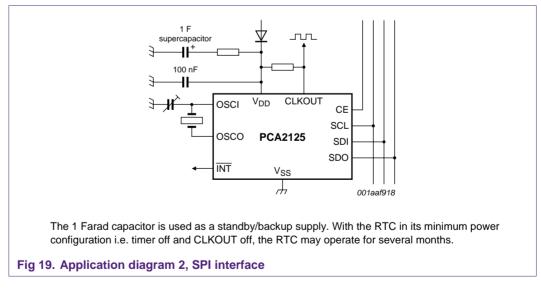

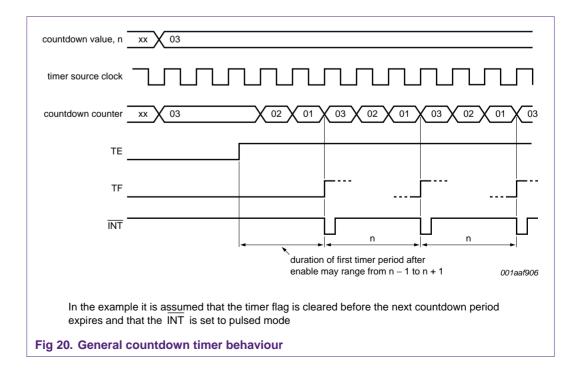

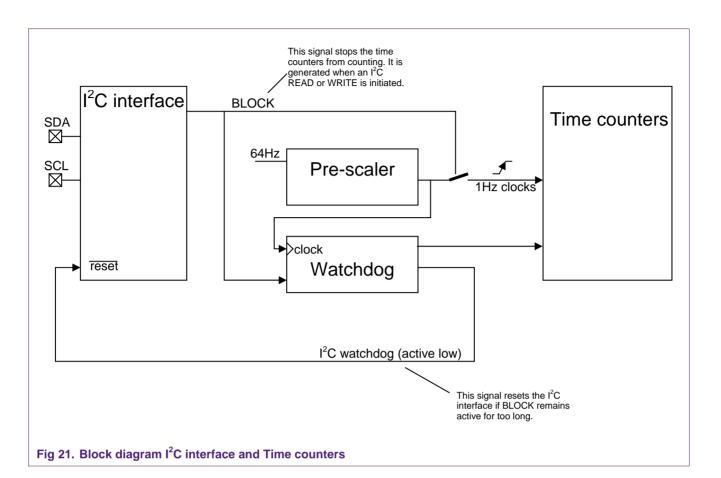

| Table 6. | Setting | the | ala | ar | m |  |